主存的地址线、容量 问题.关于计算机系统主要技术指标中内存的容量:①S=W×L(位/字节);比如S=4096×16位,1

我心永恒662022-10-04 11:39:541条回答

我心永恒662022-10-04 11:39:541条回答

主存的地址线、容量 问题.

关于计算机系统主要技术指标中内存的容量:

①S=W×L(位/字节);比如S=4096×16位,16是"字长"也就是"存储位宽"吧?有的题中字长8有的16并不一.数据线条数多少是什么决定的,是为了更细致才用乘号分开写吗,如果字长不定,那它的单位"位"是"bit"的意思吗?这里还是"8bit=1byte"吗?可以这样写吗:S=4096×16bit=4096×16/8=8192byte=8G ?

②2^(地址线根数)=存储单元个数.为什么地址线根数与存储单元个数是2的次方关系.

③对应每个字的字长=数据线条数,为什么?如2048×8位有11条地址线,8条数据线

刚学,有很多问题,一时看得迷迷糊糊晕头转向,见笑.

关于计算机系统主要技术指标中内存的容量:

①S=W×L(位/字节);比如S=4096×16位,16是"字长"也就是"存储位宽"吧?有的题中字长8有的16并不一.数据线条数多少是什么决定的,是为了更细致才用乘号分开写吗,如果字长不定,那它的单位"位"是"bit"的意思吗?这里还是"8bit=1byte"吗?可以这样写吗:S=4096×16bit=4096×16/8=8192byte=8G ?

②2^(地址线根数)=存储单元个数.为什么地址线根数与存储单元个数是2的次方关系.

③对应每个字的字长=数据线条数,为什么?如2048×8位有11条地址线,8条数据线

刚学,有很多问题,一时看得迷迷糊糊晕头转向,见笑.

已提交,审核后显示!提交回复

共1条回复

三月五日阴 共回答了18个问题

三月五日阴 共回答了18个问题 |采纳率100%- 一,存储单元的个数由地址线条数决定,比如11根线,那么共2^11个存储单元(B),这个理解吧?计算机的硬件设计决定了多少条地址线.比如个人电脑的地址总线是32位的,CPU、内存控制器、操作系统都是按32位地址总线设计.32位地址总线可以支持的内存地址空间是 2^32/1024/1024 = 4096MB,也就是有4GB的地址代码,可以编4GB个地址.

二,看“2048×8位” ,即 2^11 * 8位 ,11代表11根地址线,2^11个存储单元(地址空间),8代表一个存储单元能存储的bit数(存储位宽),也即是8条数据线同时有0或1这样的电信号传输出去.

三,容量计算:存储单元个数(地址空间)* 存储位宽/8= ** B

四,字长是CPU的主要技术指标之一,指的是CPU一次能并行处理的二进制位数(其实和内存的数据线条数一样),字长总是8的整数倍,通常PC机的字长为16位(早期),32位,64位. - 1年前

相关推荐

- 某台计算机字长16位,主存容量为64K字,采用单字长单地址指令,共有80

某台计算机字长16位,主存容量为64K字,采用单字长单地址指令,共有80

条指令.试采用直接、立即、变址、相对四种寻址方式设计指令格式. 花逐水1年前5

花逐水1年前5 -

novopgwa 共回答了17个问题

novopgwa 共回答了17个问题 |采纳率100%a+c=287d a-c=33d 所以a=160d c=127d 离心率e=c/a=127/160 OM1的中垂线y=-x+1 OM2的中垂线y=-2x+5 所以圆心为两线交点1年前查看全部

- 下列存储器速度要求最快的是 .下列存储器速度要求最快的是 .A.寄存器 B.控存 C.主存 D.Cache.

Rock青鸟1年前1

Rock青鸟1年前1 -

humanxp 共回答了18个问题

humanxp 共回答了18个问题 |采纳率83.3%A寄存器可以理解为CPU的一个地址,处理速度最快

B控存...控制存储器吧,先发控制信号再处理?/

C主存,内存.最慢的

D,缓存,比内存快

由此可见不是A就是B

B吧,因为他少见嘿嘿1年前查看全部

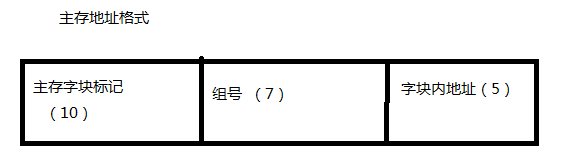

- 设某计算机的cache采用组相连映像其中每组包含四个行.已知cache的容量16kb.主存容量为

设某计算机的cache采用组相连映像其中每组包含四个行.已知cache的容量16kb.主存容量为

(续)4mb,每个行八个字,每个字32位.画出主存地址段中各段位数.回答及时的另有奖励! yu玉儿1年前1

yu玉儿1年前1 -

飘209 共回答了19个问题

飘209 共回答了19个问题 |采纳率100%1年前查看全部

- 计算机体系的问题.在一个采用组相联映象的Cache存储器中,主存由0~7共8块组成,Cache分为2组,每组2块,每块大

计算机体系的问题

.在一个采用组相联映象的Cache存储器中,主存由0~7共8块组成,Cache分为2组,每组2块,每块大小为16个存储字.在某个程序执行时,访存的主存块地址流为:6,2,4,1,4,6,3,0,4,5,7,3.

(1)写出主存块地址和Cache块地址的格式,并指出各字段的长度.

(2)采用LRU替换算法,说明该程序访存对Cache的块位置的使用情况,并计算Cache命中率. 天山麻雀1年前1

天山麻雀1年前1 -

cbd0 共回答了18个问题

cbd0 共回答了18个问题 |采纳率83.3%在一个采用组相联映象的Cache存储器中,主存由0~7共8块组成,Cache分为2组,每组2块,每块大小为16个存储字.在某个程序执行时,访存的主存块地址流为:6,2,4,1,4,6,3,0,4,5,7,31年前查看全部

- 操作系统原理题目某虚拟存储系统,用户程序空间共有32个页,每页lKB,主存为16KB.假定某时刻系统为用户的第0、l、2

操作系统原理题目

某虚拟存储系统,用户程序空间共有32个页,每页lKB,主存为16KB.假定某时刻系统为用户的第0、l、2、3页分别分配到物理块号为5、10、4、7中,试分别写出虚拟地址1234和2345的页号和页内地址,并将虚拟地址变换为物理地址. alexto9111年前1

alexto9111年前1 -

小小个的 共回答了17个问题

小小个的 共回答了17个问题 |采纳率94.1%1234的页号,页内地址为:1,210;计算方式1234-1(页号)*1024(页大小1kB)=210

同理2345为2,297;

1234的物理地址为10450;计算方法:因为1页对应10块,页的大小就是块的大小,所以块地址为10*1024(1K)=10240;块内地址同页内地址210,所以物理地址为10240+210=10450;

同理2345的物理地址为4393.1年前查看全部

- 操作系统问题已知主存有512KB容量,其中操作系统占用顶端40KB,有如下的一个作业序列:要求160KB;要求32KB;

操作系统问题

已知主存有512KB容量,其中操作系统占用顶端40KB,有如下的一个作业序列:

要求160KB;

要求32KB;

要求280KB;

完成;

完成;

要求160KB;

要求240KB;

请用首次适应算法和最佳适应算法来处理上述的作业序列,并完成以下步骤(1)~(4),要求从空白区下端分割一块作为已分配区.

(1)画出作业1、2、3进入主存后,主存的分配情况.

(2)作业1、3完成后,画出主存分配情况.

(3)画出两种算法下空白区的链接情况.

(4)哪种算法对该作业序列是适合的? qwer12981年前0

qwer12981年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 计算机组成原理(第二版)唐朔飞第73页 主存储器 有个 主存中存储单元地址分配 它举了个例子 :对24位地址线…… 这个

计算机组成原理(第二版)唐朔飞

第73页 主存储器 有个 主存中存储单元地址分配 它举了个例子 :对24位地址线…… 这个例子是否错了 没错给我解释下 w123412761年前1

w123412761年前1 -

蛮不讲理的配色 共回答了19个问题

蛮不讲理的配色 共回答了19个问题 |采纳率78.9%没有错!在4-6a中计算机的字长是4个字节;b中计算机的字长是2个字节(仔细看图).后面的你就可以理解了!

如果是自学的话几乎肯定会在这里遇到麻烦,这里的字长跟我们平时说的一个字节是8位,一个字是16位不是一个意思,它因计算机的不同而不同1年前查看全部

- 在一个虚拟存储器中,主存容量400B,划分为4页,采用LRU 页面置换算法.虚地址流为22,214,146,618,27

在一个虚拟存储器中,主存容量400B,划分为4页,采用LRU 页面置换算法.虚地址流为22,214,146,618,270,490,492,168,96,128.(1)写出虚页地址流.

(2)画出实存中的调度过程示意图(即“实存状况图”,并规定优先进入编号较小的实页) (3)写出实地址流.(4)计算命中率.

(5)假定主存的访问周期为100ns,辅存的访问周期为10ms,求系统的平均有效访问周期

要详细的解题说明,网上搜的答案我看不太懂 133552771年前1

133552771年前1 -

日中天一百 共回答了12个问题

日中天一百 共回答了12个问题 |采纳率91.7%(1)0 ,2,1,6,2,4,4,1,0,1

(2)LRU算法

0 ,2,1,6,2,4,4,1,0,1

0: 0, 0, 0,0,0 ,4,4,4,4,4

1: 2,2,2, 2, 2,2,2, 2,2

2: 1,1,1, 1,1, 1 ,1, 1

3 : 6,6, 6, 6, 6, 0, 0

(3)由上可知:虚地址流对应的实页面依次为:0,1,2,3,1,0,0,2,3,2

则实地址为:0*100+22=22,1*100+14=114,2*100+46=246,3*100+18=318,等等

(4)命中率:1-6/10=0.4

(5)书上有详解1年前查看全部

- 关于计算机原理的一道题 主存容量为256K字,Cache容量为2K字,块长为4.块长为4是说的一块有4个字吗?

关于计算机原理的一道题 主存容量为256K字,Cache容量为2K字,块长为4.块长为4是说的一块有4个字吗?

28.设主存容量为256K字,Cache容量为2K字,块长为4.x0b

(1)设计Cache地址格式,Cache中可装入多少块数据?x0b

如果块长是4表示的是一块有4个字的话 这里是不是 2048/4=512?

(2)在直接映射方式下,设计主存地址格式.x0b

按字访问的话是不是 7,9,2

256K 就是2^18 所以总共有18位 然后块内2位 Cache是512 也就是2^9 所以是9位?

(3)在四路组相联映射方式下,设计主存地址格式.x0b

这个是不是 9,7,2

(4)在全相联映射方式下,设计主存地址格式.x0b

16,2

(5)若存储字长为32位,存储器按字节寻址,

写出上述三种映射方式下主存的地址格式.

一个字有4个字节 所以存储容量是 256K*32 位 也就是 256K*4B

所以总共是 2^20B 也就是20位,是这样计算的吗?

块长就是 4*4B=2^4 所以块内是4位?

最终结果是

7,9,4

9,7,4

16,4 b ttjzpig1年前1

ttjzpig1年前1 -

strongile2008 共回答了21个问题

strongile2008 共回答了21个问题 |采纳率81%你这是自问自答吧~ 这题块长为4 这句估计就理解为4个字吧~~~如果这样理解 你的答案就都是对的1年前查看全部

- 计算机原理题主存为512M,页面大小4K,则物理页号是主存地址的高多少位?这个怎么算?

ddm_20031年前1

ddm_20031年前1 -

06pb 共回答了24个问题

06pb 共回答了24个问题 |采纳率100%512*1024/4=20000H 18位1年前查看全部

- 2.某台计算机字长16位,主存容量为64K字,采用单字长单地址指令,共有64条指令.试采用直接、立即、变址、相对四种寻址

2.某台计算机字长16位,主存容量为64K字,采用单字长单地址指令,共有64条指令.试采用直接、立即、变址、相对四种寻址方式设计指令格式.

ii何处有芳草呢1年前1

ii何处有芳草呢1年前1 -

海鸟之鹰 共回答了12个问题

海鸟之鹰 共回答了12个问题 |采纳率91.7%操作码OP 6位 | 控制X 2位 | 地址码8位

X=00,01,10,11选择寻址方式1年前查看全部

- 操作系统页面调度某虚拟存储器共有8个页面,每页为1024个字,实际主存为:4096个字,采用页表示法表示地址映像表的内容

操作系统页面调度

某虚拟存储器共有8个页面,每页为1024个字,实际主存为:4096个字,采用页表示法表示地址映像表的内容见表:

实页码 装入位

3 1

1 1

2 0

3 0

2 1

1 0

0 1

0 0

列出会发生页面失效的全部虚页号为___

按现有1023虚拟地址,下列___是其对应的主存实地址.

A.4095 B.1023 C.1024 D缺页

冷冰寒烟1年前1

冷冰寒烟1年前1 -

悲伤的蒲公英 共回答了12个问题

悲伤的蒲公英 共回答了12个问题 |采纳率83.3%某虚拟存储器共8个页面,每页1024个字,实际主存为4096个字,采用页表法进行地址映象。映象表的内容如下表1所示。实页号 装入位

3 1

1 1

2 0

3 0

2 1

1 0

0 1

0 0

表1 虚页号 实页号 装入位

0 3 1

1 1 1

2 2 0

3 3 0

4 2 1

5 1 0

6 0 1

7 0 0

表2 (1)列出会发生页面失效的全部虚页号;

根据页表法列出表2,当装入位为0时,即为页面失效,再找出相对应的虚页号即可。

会发生页面失效的全部虚页号为:2,3,5,7

(2)按以下虚地址计算主存实地址:0,3728,1023,1024,2055,7800,4096,6800。

虚页号=│_虚地址/页面大小_│

实地址=(实页号*页面大小)+(虚地址-虚页号*页面大小) 虚地址 0 3728 1023 1024 2055 7800 4096 6800

虚页号 0 3 0 1 2 7 4 6

实页号 3 3 3 1 2 0 2 0

装入位 1 0 1 1 0 0 1 1

实地址 3072 3728 4095 1024 2055 632 2048 6561年前查看全部

- 计算机组成原理寻址问题唐硕飞《计算机组成原理》73页对24位地址线的主存而言,字长为32的IBM370机按字节寻址范围是

计算机组成原理寻址问题

唐硕飞《计算机组成原理》73页对24位地址线的主存而言,字长为32的IBM370机按字节寻址范围是16M按字寻址为4M,而字长为16位的PDP—11机按字节寻址范围为16M,按字寻址范围为8M.

这段话怎么理解,数字是怎么计算的比如16M指的是16兆字节还是16兆位

另外,组成原理先修课程有哪些? 哓哓本1年前1

哓哓本1年前1 -

阿芸 共回答了11个问题

阿芸 共回答了11个问题 |采纳率100%首先你要知道,寻址范围是和地址线有关系的,字长是和数据线有关系的,所以16M就是2的24次方,这是按字节寻址的,如果是按字寻址的话,因为一个32位的字长是4个字节,所以要在按字节寻址的基础上除以4,这就是IBM370.PDP—11也是这个道理,按字节寻址16M,按字寻址就要除以2,因为16位是两个字节.

组成原理要学好挺不容易的,1年前查看全部

- 计算机组成原理 计算题某主存容量为1MB,用128K×4的RAM芯片组成.请解答下列问题.1,应该使用多少片芯片?采用什

计算机组成原理 计算题

某主存容量为1MB,用128K×4的RAM芯片组成.请解答下列问题.

1,应该使用多少片芯片?采用什么连接方式?

2,分成几组?组内含多少芯片?

3,需要地址总线多少根?数据总线多少根?

4,有多少地址总线是连接到芯片的地址输入端的?有多少地址总线是经过译码器输出到芯片片选的?

谢谢~

yuan7891年前1

yuan7891年前1 -

balidao 共回答了21个问题

balidao 共回答了21个问题 |采纳率85.7%16片,字位同时扩展

8组,每组2片

地址20根,数据8根

17根,3根1年前查看全部

- cache命中率计算公式?求cache命中率计算公式,就是已知主存和cache的访问时间,然后计算出cache的命中率,

cache命中率计算公式?

求cache命中率计算公式,就是已知主存和cache的访问时间,然后计算出cache的命中率,那公式在操作系统里有的,可惜现在我手头上没有操作系统课本,想请朋友能给我发上来! 香芋小布丁1年前1

香芋小布丁1年前1 -

zhouwei760109 共回答了17个问题

zhouwei760109 共回答了17个问题 |采纳率82.4%Cache命中率=(平均存取时间-主存存取时间)/(高速缓存存取时间-主存存取时间)

书上是这么说的:

Ta=HTa1+(1-H)Ta2

Ta为平均存取时间,Ta1为Cache的存取时间,Ta2为主存存取时间,H为Cache命中率.

换算一下就得到了.1年前查看全部

- cache命中率设某机主存容量为4MB,Cache容量为16KB,每字块有8个字,每字32位,设计一个四路组相连映像(即

cache命中率

设某机主存容量为4MB,Cache容量为16KB,每字块有8个字,每字32位,设计一个四路组相连映像(即Cache每组内共有4个字块)的Cache组织,要求:(1) 画出主存地址字段中各段的位数;

(2) 设Cache的初态为空,CPU依次从主存第0,1,2……99号单元读出100个字(主存一次读出一个字),并重复按此次序读8次,问命中率是多少?

(3) 若Cache的速度是主存的6倍,试问有Cache和无Cache相比,速度提高多少倍?

小歌一首1年前1

小歌一首1年前1 -

笑完就哭 共回答了13个问题

笑完就哭 共回答了13个问题 |采纳率92.3%这些你要先了解 1.指令的读取首先访问cache,cache没有的话再访问主存 2.指令的访存总时间=指令访存cache的总时间+指令访存主存的总时间 3. 指令访存n1年前查看全部

- 在GB2312-80标准中,一个汉字在计算机主存中存储需要2个字节,一篇8000字的文章存储在计算机内存需要多大的内存空

在GB2312-80标准中,一个汉字在计算机主存中存储需要2个字节,一篇8000字的文章存储在计算机内存需要多大的内存空间?存储8000字的英文文章需要多大内存空间

dihdhd1年前1

dihdhd1年前1 -

女生张芝若 共回答了22个问题

女生张芝若 共回答了22个问题 |采纳率100%位是计算机存储最小的单位,一个字节即1B(Byte)等于8位(bit),1KB=1024bit,1MB=1024KB,1GB=1024MB,因此8000字不包含标点符号,就是8000*2=16000字节(Byte),大约是16000/1024=16KB.即通常所说的16K的空间.1年前查看全部

- 设某计算机的cach采用4路组相联映像,已知cache的容量为16KB,主存容量为2MB,

设某计算机的cach采用4路组相联映像,已知cache的容量为16KB,主存容量为2MB,

每个字块有8个字,每个字有32位.解得,主存地址21位 区号 7位 组号 7位 块号 2位 块内地址 3位 字节 2位 问题是什么时候要计算到字节的位数啊,看一些题只算到块内地址, wade211年前1

wade211年前1 -

天地男儿2007 共回答了18个问题

天地男儿2007 共回答了18个问题 |采纳率88.9%题目问的是什么 求解要看题目问到哪里1年前查看全部

- 操作系统的题 不会啦!求助!某基于动态分区存储管理的计算机,其主存容量为55mb(初试为空间),采用最佳适配(Best

操作系统的题 不会啦!求助!

某基于动态分区存储管理的计算机,其主存容量为55mb(初试为空间),采用最佳适配(Best fit)算法,分配和释放的顺序为:分配15mb,分配30mb,释放15mb,分配8mb,此时主存中最大空闲分区的大小是( )

A:7mb B:9mb C:10mb D:15mb

杏黄小肚兜1年前2

杏黄小肚兜1年前2 -

sherian 共回答了18个问题

sherian 共回答了18个问题 |采纳率94.4%其主存容量为55mb(初试为空间),第一步分配15MB以后还有55MB-15MB=40MB,第二步分配30MB以后还有40MB-30MB=10MB,第三步释放15MB以后有两个空闲区15MB,和10MB,第四步分配8MB,则空闲区为15MB,2MB,第五步分配6MB,则空闲区为9MB,2MB,所以这个题目应该是选B1年前查看全部

- 计算机组成与系统结构作业题假设主存只有 a,b,c 三个页框,组成 a 进 c 出的 FIFO 队列,进程访问页面的序列

计算机组成与系统结构作业题

假设主存只有 a,b,c 三个页框,组成 a 进 c 出的 FIFO 队列,进程访问页面的序列是

8,4,5,6,4,8,6,4,8,8,6,4 号.用列表法求采用 FIFO+LRU 替换策略时的命中率. moyan791年前0

moyan791年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 设某计算机主存容量为64K字,Cache存储器的容量为512字,字块长128字,采用直接映象方式和LRU替换算法.

设某计算机主存容量为64K字,Cache存储器的容量为512字,字块长128字,采用直接映象方式和LRU替换算法.

1、 求出主存空间块数.

2、 画出主存储器和Cache存储器字块对应关系图和主存地址字段划分图,标出名段位数. Wanhuajituan1年前1

Wanhuajituan1年前1 -

钻石hh 共回答了18个问题

钻石hh 共回答了18个问题 |采纳率88.9%这道题的两问与LRU(最近最少使用)替换算法无关.

1、由主存总容量为64K字,每个字块长128字,所以主存空间块数为64K/128=2的9次方.

2、主存储器和Cache存储器字块对应关系图我就不画了,你们教材上肯定有.

主存地址分为三段,高7位为区地址,中间2位为区内块地址,最后7位为块内偏移量.

由每个字块长128字,得块内偏移量为7位.

由cache中块数为512字/128字=2的2次,得主存每区内块地址为2位.

最后区地址为16位-2位-7位=7位.1年前查看全部

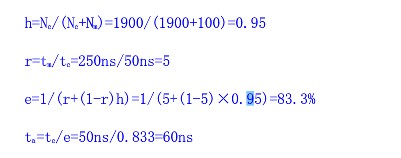

- 一道计算机的题CPU 执行一段程序时,cache完成存取的次数为1900次,主存完成存取的次数为100次,已知cache

一道计算机的题

CPU 执行一段程序时,cache完成存取的次数为1900次,主存完成存取的次数为100次,已知cache存取周期为50ns,主存存取周期为250ns,求cache/主存系统的效率和平均访问时间

我这里有两种算法,算出来答案都一样,是不是两种算法都是对的呢?

平均访问时间=(1900*50+100*250)/(1900+100)

=60s

cache主存系统效率=cache存取周期/平均访问时间

=50/60

=83.3%

王oo1年前1

王oo1年前1 -

一千年以后1 共回答了9个问题

一千年以后1 共回答了9个问题 |采纳率100%正确无误.1年前查看全部

- 计算机原理问题要求画出主机框图,分别以存数指令“STA M”和加法指令“ADD M”(M均为主存地址)为例,在图中按序标

计算机原理问题

要求画出主机框图,分别以存数指令“STA M”和加法指令“ADD M”(M均为主存地址)为例,在图中按序标出完成该指令(包括取指阶段)的信息流程.假设贮存容量为256M*32位,在指令字长、存储字长、机器字长相等的条件下,指出图中各寄存器的位数. 反町隆史shi1年前1

反町隆史shi1年前1 -

CharlesHsieh 共回答了22个问题

CharlesHsieh 共回答了22个问题 |采纳率77.3%1年前查看全部

- 求解计算机组成原理题某机字长为16位,主存容量为64K字,采用单字长单地址指令,共有50条指令.若有直接寻址、间接寻址、

求解计算机组成原理题

某机字长为16位,主存容量为64K字,采用单字长单地址指令,共有50条指令.若有直接寻址、间接寻址、变址寻址和相对寻址4种寻址方式,试设计其指令格式 四楼的风1年前1

四楼的风1年前1 -

guangtang 共回答了12个问题

guangtang 共回答了12个问题 |采纳率100%你按照这个解答就行了,下面的如果你不是很清楚,我可以以WORD.doc的格式直接发到你的QQ邮箱里面

某计算机字长为16位,主存容量为64K字,采用单字长单地址指令,共有40条指令.试采用直接、立即、变址、相对四种寻址方式设计指令格式.

答:根据题意,40种指令至少需6位OP;四种寻址方式至少需用2位表示;主存为640K,则地址需要20位,而机器字长为16位,所以只能用分段方式来实现,设段寄存器为16位,作为段内地址的位移量可以在指令指定的寄存器中,可设计如下格式:

15 10 9 8 7 0

OPx05X(2)x05D(8)

X = 00 直接寻址方式 E = D

X = 01 立即寻址方式

X = 10 变址寻址方式 E = (R)+D

X = 11 相对寻址方式 E = (PC)+D1年前查看全部

- 分页式存储管理系统中,主存容量为1M

分页式存储管理系统中,主存容量为1M

假定某采用分页式虚拟存储系统中,主存储容量为1M,被分为256份,块号为0、1、2……255.某作业的地址空间占4页,页号为0,1,2,3,被分配要主存的第2,4,1,5块中,回答

(1)主存地址应该用是____位来表示

(2)作业每一页的长度为_____,逻辑地址中的页内地址(单元号)占用____位

答案为(1)20(2)4K,12

请给出解题思路, wollsor1年前1

wollsor1年前1 -

qqq4321 共回答了22个问题

qqq4321 共回答了22个问题 |采纳率100%1M=1024K/M*1024B/K=2^20B

1M=1024K 1024k/(255+1)=4k

4k=4*1024b/k=2^121年前查看全部

- 常用的主存单元寻址方式有哪些?写出其中任意四种寻址方式计算有效地址(EA)的表达

sun手心1年前1

sun手心1年前1 -

媛媛生气了 共回答了17个问题

媛媛生气了 共回答了17个问题 |采纳率88.2%ea:操作数的偏移地址.

除了寄存器寻址 貌似别的都可以吧

如:mov ax, ;间接寻址

mov ax,;直接寻址

mov ax,;相对寻址

等等.1年前查看全部

- 关于Cache命中率假如某流水线计算机主存的读/写时间为100ns,有一个指令和数据合一的Cache,已知该Cache的

关于Cache命中率

假如某流水线计算机主存的读/写时间为100ns,有一个指令和数据合一的Cache,已知该Cache的读/写时间为10ns,取指令的命中率为98%,取数据的命中率为95%。在执行某类程序时,约有1/5指令需要存/取一个操作数。假设指令流水线在任何时候都不阻塞,则设置Cache后,每条指令的平均访存时间约为多少?

答案为

(2%*100ns+98%*10ns)+1/5(5%*100ns+95%*10ns)=14.7ns

能有谁知道这个解答思路,那几个数据怎么来的,为什么要这么算呢。

mimimiaomiao1年前1

mimimiaomiao1年前1 -

Starry__Sky 共回答了15个问题

Starry__Sky 共回答了15个问题 |采纳率86.7%这些你要先了解

1.指令的读取首先访问cache,cache没有的话再访问主存

2.指令的访存总时间=指令访存cache的总时间+指令访存主存的总时间

3.

指令访存cache的总时间=指令取出cache的时间+数据取出cache的时间

指令访存主存的总时间=指令取出主存的时间+数据取出主存的时间

4.每条指令的平均访存时间

=每条指令的平均取指令时间+每条指令的平均取数据时间

=(每条指令平均取出cache的时间+每条指令平均取出主存的时间)

+(每条指令数据平均取出cache时间+每条指令数据平均取出主存的时间)

如果还不明白,就不要考了1年前查看全部

- 已知某计算机字长8位,其主存的地址码为20位,若使用4K×4位的SRAM芯片组成该机所允许的最大主存空间,并使用模块结构

已知某计算机字长8位,其主存的地址码为20位,若使用4K×4位的SRAM芯片组成该机所允许的最大主存空间,并使用模块结构形式.问:(1)若每个模块为64K×8位,共需几个模块?(2)每个模块内应有多少RAM芯片?(3)主存共需多少RAM芯片?

木将子1年前1

木将子1年前1 -

jason1215 共回答了18个问题

jason1215 共回答了18个问题 |采纳率94.4%(1) 内存总量需要2^20,也就是1024K×8位,一个模块是64K×8位,所以一共需要1024/64=16个模块

(2)一个芯片4K×4位,两个芯片才能组成4K×8位,要组成64K×8位则需要64/4×2=16×2=32片

(3)共需要32×16=512片1年前查看全部

- 某32位微型计算机中,存储器容量为1MB,若按字节编址,那么主存的地址寄存器至少应有().A.20;B.24;C.32;

某32位微型计算机中,存储器容量为1MB,若按字节编址,那么主存的地址寄存器至少应有().A.20;B.24;C.32;D.16;

A.20

请问原理是什么呀,.. cjhuang1年前1

cjhuang1年前1 -

baoshan0007 共回答了14个问题

baoshan0007 共回答了14个问题 |采纳率85.7%容量1MB,按照字节(也就是1B)编制,那么地址空间应该为1MB/1B=1Mb.

B是字节,b是比特.1B=8b.

既然地址空间为1Mb(1兆比特),1Mb=2的20次方,所以主存的地址寄存器至少应有20.

再举个例子,如果按照双字编制,双字为2B,那么地址空间应该为1MB/2B=500kb(或是512kb),512kb=2的19次方,主存的寄存器应至少有19.

明白了么?1年前查看全部

- 计算机系统结构,求详解~有一个Cache存贮器,块的大小为512字(字为最小编址单位),主存分8块,Cache分为4块,

计算机系统结构,求详解~

有一个Cache存贮器,块的大小为512字(字为最小编址单位),主存分8块,Cache分为4块,采用组相联映象(组间直接、组内相联),每组2块,替换算法为LRU。

(1)标出主存、Cache地址的各字段位数。

(2)画出主存、Cache空间块映象对应关系图。

(3)设主存块地址流为1、2、4、1、3、7、0、1、2、5、4、6、4、7、2,

从Cache为空开始,列出Cache中各块随时间的使用状况。

(4)需要进行块替换的时刻有哪些?

(5)求Cache的命中率。

elecfans1年前0

elecfans1年前0 -

共回答了个问题

共回答了个问题 |采纳率

- 计算机组成原理1.在cache的地址映射中,若主存中的任意一块均可映射到cache内的任意一块的位置上,则这种方法称为_

计算机组成原理

1.在cache的地址映射中,若主存中的任意一块均可映射到cache内的任意一块的位置上,则这种方法称为_________。

A. 全相联映射 B. 直接映射

C. 组相联映射 D. 混合映射

2.若使8 bit寄存器A最高位清0,可采用________;

A. B.

C. D.

3.微程序存放在________中。

A. 控制存储器 B. RAM

C. 指令寄存器 D. 内存储器

4.微周期指的是________所需要的时间;

A. 执行一条微命令 B. 执行一条微指令

C. 执行一段微程序 D. 执行一条机器指令

1. CPU中,保存当前正在执行的指令的寄存器为_______________,保存下条指令地址的寄存器为_______________,保存CPU访存地址寄存器为_________________。

2. 计算机系统中的存储器分为___________和___________。在CPU执行程序时,必须将指令存放在___________中。

3. 在同一微周期中_________________的微命令,称之为互斥的微命令;在同一微周期中__________________的微命令,称之为相容的微命令。显然,__________________不能放在一起译码。

4. 计算机存储器的最小单位为_____________,1KB容量的存储器能够存储_____________个这样的基本单位。

5. 对存储器的要求是____________、_____________、_____________;为了解决这三方面的矛盾,计算机采用_____________体系结构。

6. 指令的格式是由______________和_______________组成的。

7. 计算机指令系统往往具有多种寻址方式,操作数就是指令的一部分称为___________寻址,操作数地址在指令中称为_____________寻址,当操作数地址在寄存器中,就采用_____________寻址方式。

8. 在寄存器间接寻址方式中,有效地址存放在_____________中,而操作数存放在_____________中。

9. 在机器的一个CPU周期中,一组实现一定操作功能的微命令的组合,构成一条_____________,它由_____________和_____________两部分组成。

10. 微程序控制器的核心部件是___________,它是一种__________存储器。

11. CPU周期也称为____________,一个CPU周期包含若干个____________。

xiaohe69151年前2

xiaohe69151年前2 -

mylvyao 共回答了18个问题

mylvyao 共回答了18个问题 |采纳率83.3%1.a

2.没选项 。。。

3.a

4.c

1. PC程序计数器 IR指令寄存器 内存地址寄存器AR

2.1)主存储器(2)辅助存储器 主存储器

3.指不能同时或不能在同一个节拍内并行执行的微操作。可以编码

指能够同时或在同一个节拍内并行执行的微操作。必须各占一位

不知道

4.位

5.容量大、速度快、成本低 分级存储器结构

6.操作码 地址码

7.立即寻址 不知道 隐含寻址

8.寄存器中 主存单元的地址号

9.微指令 操作控制 顺序控制

10.控制存储器(CM) 来存放微程序. 来存放微程序

11.机器周期 子指令周期

纯手工打造1年前查看全部

- 设某计算机的cache采用4路组相连映像,已知cache的容量为1KB,主存总量为1MB,每个字块有

设某计算机的cache采用4路组相连映像,已知cache的容量为1KB,主存总量为1MB,每个字块有

16个字,每个字有32位,请回答,主存地址共有多少位,主存地址字段中主存字块标记,组地址标记和块内地址各需多少位 smartfat1年前3

smartfat1年前3 -

zhang2881682 共回答了17个问题

zhang2881682 共回答了17个问题 |采纳率94.1%每个子块有16*32/8=64字节,即1MB主存内有1048576/64=16384个字块,14位就行了.4路组相连只要2位就行了.cache内有1024/64=16个字块,4位就行了.所以主存地址段中主存字块标记需要14位,组地址标记需要2位,快内地址需要4位.1年前查看全部

- 问一个有关cache——主存地址映射的问题,

问一个有关cache——主存地址映射的问题,

有一道例题题目是这样的,假设主存容量是512kb,cache容量是4kb,每个字块为16个字,每个字32位.问cache中有几个字块.

书上的解答是由于每字32位,则cache共有4kb/4b=1k字.因每个字块16个字,所以cache中有1k/16=64块.

我认为,cache有4kb的容量,就肯定是有4kb个字,除以16个字,就应该有256块,为什么4kb还要除以4b. kerrzhang03021年前1

kerrzhang03021年前1 -

洁韵 共回答了20个问题

洁韵 共回答了20个问题 |采纳率85%楼主理解有问题,4kb的容量不等于4kb个字,是4k个字节,一字节为8位.

一个字32位,32位就是4个字节4b.

4kb/4b就是cache共有多少个字,为1k个字.

一个字块16个字,1k/16就是多少个字块.

我靠,才发现,一点悬赏都没有!1年前查看全部

- 某机字长为32位,其存储容量是64KB,按字编址其寻址范围是多少?若主存以字节编址,试画出主存字地址和字

鑫泽1年前1

鑫泽1年前1 -

bird_qq 共回答了15个问题

bird_qq 共回答了15个问题 |采纳率93.3%=8bit=1B 2^20B/1B = 2^20 地址范围为0~2^20-1 也就是说至少需要二十根地址线,地址寄存器是用来存放地址的,与存储器容量及编址方式有关,可以简单的认为地址线的个数等于地址寄存器的位数,所以地址寄存器为20位.

2、数据寄存器用来存放CPU在一个存取周期内从存储器中一次性取出为二进制位数,也就是一个机器字长,本题中字长32位,所以数据寄存器为32位.

3、寻址空间.在此需要区分清楚寻址空间与寻址范围两个不同的概念,范围仅仅是一个数字范围,不带有单位,而寻址空间指能够寻址最大容量,单位一般用MB、B来表示;本题中寻址范围为0~2^20-1,寻址空间为1MB.

想必是报考计算机专业的研友,如果还不太清楚,可以HI我.1年前查看全部

- 计算机原理的题,请指教已知某8位机的主存采用半导体存储器,地址码为18位,采用4K×4位的SRAM芯片组成该机所允许的最

计算机原理的题,请指教

已知某8位机的主存采用半导体存储器,地址码为18位,采用4K×4位的SRAM芯片组成该机所允许的最大主存空间,并选用模块条形式,问:

(1) 若每个模块条为32K×8位,共需几个模块条?

(2) 每个模块条内有多少片RAM芯片?

(3) 主存共需多少RAM芯片?CPU需使用几根地址线来选择模块?使用何种译码器?

alexpuqin1年前1

alexpuqin1年前1 -

胡要邦 共回答了16个问题

胡要邦 共回答了16个问题 |采纳率62.5%(1)地址码18位,8位机,所以最大主存空间为(256×8)KB

所以需用模块数为(256×8)/(32×8)= 8

(2)4K×4位的SRAM芯片,构成32K×8位的模块条,需(32K×8位)/4K×4位=16,即需8组SRAM,每组2条,才能构成一个模块条

(3)共需8×16=128个RAM芯片

8个模块条,所以3条(2^3)地址线来片选模块

译码器选用...1年前查看全部

- 已知Cache存储周期40ns,主存存储周期200ns,Cache/主存系统平均访问时间为50ns,求Cache的命中率

已知Cache存储周期40ns,主存存储周期200ns,Cache/主存系统平均访问时间为50ns,求Cache的命中率是多少?

晌午的月亮1年前1

晌午的月亮1年前1 -

倒走时钟 共回答了24个问题

倒走时钟 共回答了24个问题 |采纳率83.3%50=40r+200(1-r) r=15/161年前查看全部

- 操作系统,页面淘汰算法!急用,某虚拟存储系统采用最近最少使用(LRU)页面淘汰算法,假定系统为每个作业分配3个页面的主存

操作系统,页面淘汰算法!急用,

某虚拟存储系统采用最近最少使用(LRU)页面淘汰算法,假定系统为每个作业分配3个页面的主存空间,其中一个页面用用来存放程序.现有某作业的部分语句如下:

Var A:Array[1...150,1...100] of integer;

i,j:interger;

for i=1 to 150 do

for j=1to 100 do a [i,j]=0;

设每个页面可存放150个证书变量,变量i,j放在程序页中.初始时,程序及变量i,j已经在内存,其余两页为空,举证A按行序存放.在上述程序片段执行过程中,公产生( )次缺页中断.

我看不到你发的链接,而且解压码也看不到啊. 金莲三寸1年前1

金莲三寸1年前1 -

毛毛19850220 共回答了20个问题

毛毛19850220 共回答了20个问题 |采纳率95%100

每页可以放150变量,而二维数组按行存储,所以数组三行可以存入两页中,150行存入100页中.循环也是按行操作,也就是每页中的变量依次处理,各页都在全处理完成后转入下一页处理(缺页中断),每页只会发生一次缺页中断,所以缺页中断数为100.

程序段所在页一直使用,所以在LRU算法中不会被淘汰.另外两个页面在一段时间内只会使用一个页面,直到它里面的变量全处理完成,所以淘汰算法会淘汰另外一页用以装入新页,故不会造成额外的缺页.1年前查看全部

- 组成原理习题求解某计算机系统的主存采用32位字节地址空间和64位数据线访问存储器,若使用64M位的DRAM芯片组成该机所

组成原理习题求解

某计算机系统的主存采用32位字节地址空间和64位数据线访问存储器,若使用64M位的DRAM芯片组成该机所允许的最大主存空间,并采用内存条的形式.若每个内存条为64M*32位,共需多少内存条?

答案为何是16条? jinxuyang111年前1

jinxuyang111年前1 -

SunSeason_JC 共回答了14个问题

SunSeason_JC 共回答了14个问题 |采纳率100%这里面关键是这句话:计算机系统的主存采用32位字节地址空间,也就是说按字节编址,可以有2^32个字节单元;但系统采用64位数据线访问存储器,即一次访存,可以读取64位=8个字节,占用8个字节单元地址.所以,按照64位编址的地址单元数应该是:2^32/8=2^29

则总的存储容量=2^29*64位

每个内存条容量=64M*32位=2^26*32位

2^29*64

-----------=2^4=16条

2^26*32

所以,共需16条这样的内存条.1年前查看全部

- 一个直接映象的cache由32个存储块组成,主存包含2048个存储块,每块32个字

一个直接映象的cache由32个存储块组成,主存包含2048个存储块,每块32个字

1.求主存地址位数?cache地址的位数?

2.主存地址中字块标记,块号,块内地址咋算 blueld1年前1

blueld1年前1 -

采姑娘的小蘑菇啊 共回答了19个问题

采姑娘的小蘑菇啊 共回答了19个问题 |采纳率94.7%主存位数16

cache的位数 6

标记位是6 块号是4 块内地址是61年前查看全部

- 假设在一个采用组相联映像方式的Cache中,存储器按字节编址,主存由M0~M63共64页组成,Cache由C0~C7共8

假设在一个采用组相联映像方式的Cache中,存储器按字节编址,主存由M0~M63共64页组成,Cache由C0~C7共8页组成,分成4组(每组2页),每页大小为16字节.

1.写出主存地址的格式,并标出各字段的长度;

2.画出主存与Cache之间各个页的映像对应关系;

3.说明主存地址为0ABH的字节单元应映像到Cache的哪个页中? 秋名山车神1年前1

秋名山车神1年前1 -

当wo遇见ni 共回答了26个问题

当wo遇见ni 共回答了26个问题 |采纳率80.8%主存地址:64*16=2^10,所以主存地址是10位;字节号:16=2^4,需要4位;块号:4=2^2,需要2位;组号(页面号):2=2^1,需要1位;区号:10-4-2-1=3位;1.主存地址格式和各部分长度:2.主存和cache对应关系:上面是主存,...1年前查看全部

- 计算机组成原理的一题.已知cache / 主存系统效率为85% ,平均访问时间为60ns,cache 比主存快4倍,求主

计算机组成原理的一题.

已知cache / 主存系统效率为85% ,平均访问时间为60ns,cache 比主存快4倍,求主存储器周期是多少?cache命中率是多少? 一土日木1年前1

一土日木1年前1 -

小毛点 共回答了21个问题

小毛点 共回答了21个问题 |采纳率85.7%h=命中率;Ta=平均访问时间;e=效率;

Tm=主存周期;Tc=Cache访问时间;

e=Tc/Ta=0.85

Ta=h*Tc+(1-h)Tm=60ns

Tm=4Tc

解得:Tc=51ns; Tm=204ns; h=16/17;1年前查看全部

- 在8086中,主存的物理地址由哪部分组成?每个段与寄存器之间有何对应的要求?

煊子1年前1

煊子1年前1 -

海边暮色 共回答了18个问题

海边暮色 共回答了18个问题 |采纳率94.4%20位物理地址由16位段地址和16位偏移地址组成,物理地址的计算方法可以表示如下:16d×段地址+偏移地址=物理地址

代码段的段地址放在CS中,数据段的段地址放在DS中,堆栈段的段地址放在SS中,附加段的段地址放在ES中.1年前查看全部

- 在Cache的地址映射中,若主存中的任意一块只能映射到Cache存储体的特定行

在Cache的地址映射中,若主存中的任意一块只能映射到Cache存储体的特定行

则,该种映射方式是

A.全相联 B.组相联 C.直接映射 D.混合映射. 一宽眼界1年前1

一宽眼界1年前1 -

霄汉居士 共回答了15个问题

霄汉居士 共回答了15个问题 |采纳率100%A吧,像这种题吧,书上应该有呀!1年前查看全部

- 在Cache映射里的组相联映射,是每一组共有一个主存字块标记还是组里的每一块都有一个主存字块标记

在Cache映射里的组相联映射,是每一组共有一个主存字块标记还是组里的每一块都有一个主存字块标记

还有有效位是每组共有一个,还是组里的每一块都有一个呢

西西拉拉1年前1

西西拉拉1年前1 -

我顶过你的贴 共回答了25个问题

我顶过你的贴 共回答了25个问题 |采纳率92%你说的组我理解是cache line, 每一个cache line里面有若干数据(应该是你说的字块吧).应该是每一个cache line有个一个tag(标记),字块查找是通过地址后几位来完成的.可以参阅http://blog.csdn.net/pang040328/article/details/4285590.1年前查看全部

大家在问

- 1make from与make with的区别是什么?

- 21/sin^2 10°-3/cos^2 10°=32cos20°

- 3(2013•北京)关于高中生物学实验的基本原理,叙述不正确的是( )

- 4“感谢老师的信任”为作文题目,必采纳!要快点!

- 5懒惰的反义词用英语怎么说

- 6英语选择题(2道,要原因)With the help pg computers,we can do some work_

- 7给母校,老师,同学写下祝福、感激的话语各两句(运用修辞)

- 8英语翻译if the general inflation rate between year 4and year 4 w

- 9一氧化碳与水在常温下能反应吗?

- 10宋代理学被称为“新儒学”、指出其突出特点

- 11鲁滨逊漂流记中鲁滨逊造的船有没有下水

- 12写带有万和千的成语如万水千山还有什么

- 13五年级下册数学概念1到6单元

- 14我们教室前的墙上有两张画(用英语怎么说

- 15这种计算器怎么算方差和平均数?最好是举个例子,